Architecture Overview

Deep dive into the MHX™ Ternary RISC-V Core architecture and design decisions.

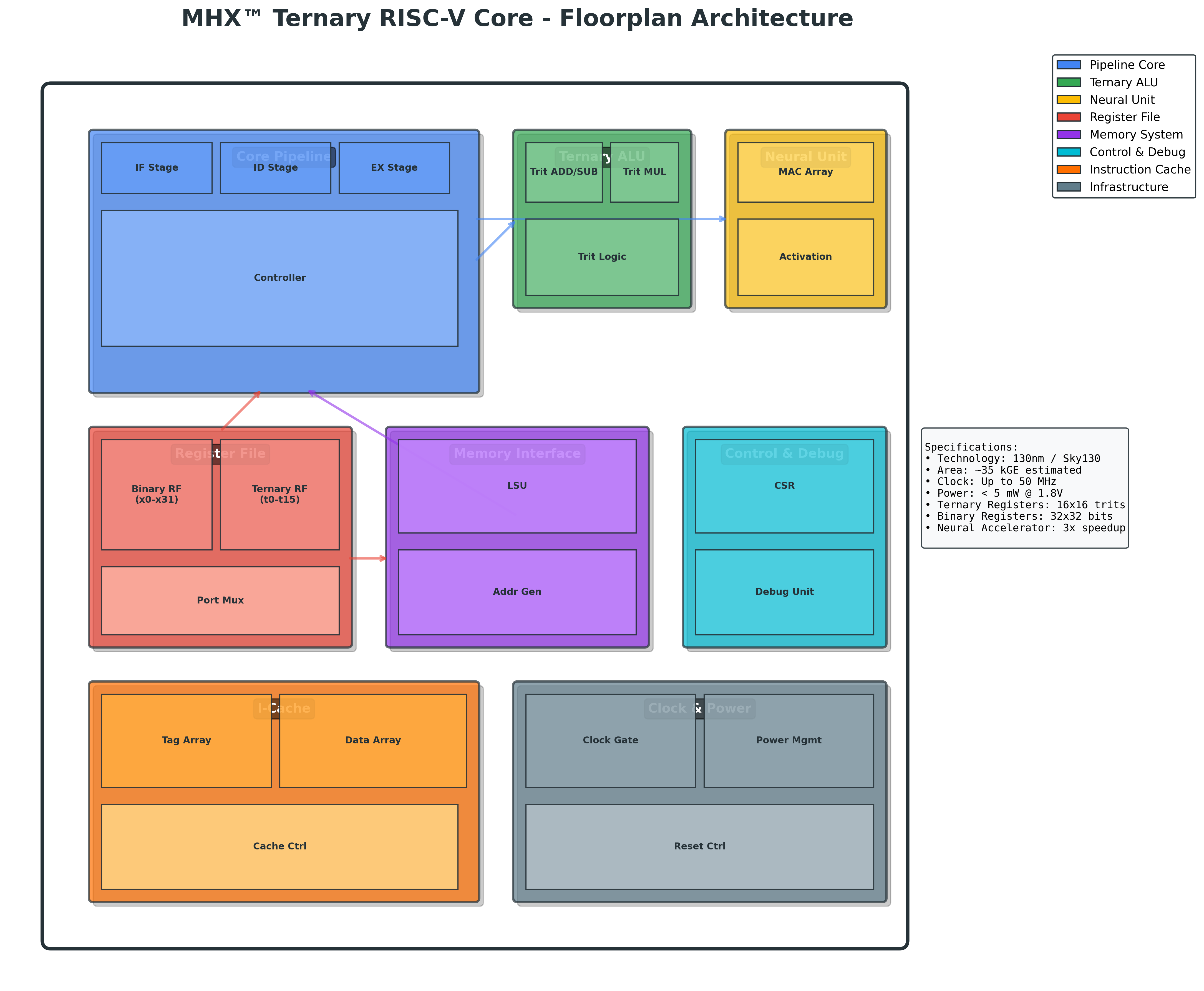

Floorplan

Complete floorplan showing all major functional blocks and interconnections

Core Components

Ternary ALU

Native 16-trit arithmetic and logic unit with overflow detection

Neural Unit

Hardware-accelerated neural network operations with MAC arrays

Register File

Dual register file: 32 binary + 16 ternary registers

Pipeline Integration

Seamless integration with standard Ibex 2-stage pipeline

Design Philosophy

1. Minimal Impact on Base Core

The MHX™ extension is designed to minimize changes to the base Ibex core. All ternary functionality is isolated in separate modules that can be conditionally included.

2. Native Ternary Operations

Rather than emulating ternary logic in binary, the core implements true ternary arithmetic at the hardware level, enabling significant efficiency gains.

3. Neural Network Acceleration

The neural unit provides hardware acceleration for the most common TNN operations, achieving up to 3x speedup compared to software implementations.

Key Specifications

| Feature | Specification |

|---|---|

| Base ISA | RV32IMC |

| Ternary Registers | 32 registers (T0-T31) × 16 trits each (32 bits per register) |

| Ternary Operations | 15 operations (7 core + 8 advanced) |

| Neural Unit Pipeline | 3-stage pipelined (MAC, activation, normalization) |

| Weight Cache | 16-entry LRU cache (70% bandwidth reduction) |

| Target Frequency | Up to 250 MHz (pipelined design) |

| Area Overhead | ~0.15 mm² @ 65nm (complete ternary extension) |

| Power (estimated) | ~15 mW @ 100 MHz (neural inference) |

| Throughput | 16 ternary MACs per cycle |

Memory Subsystem

The core supports both traditional binary memory access and optional optimized ternary memory interface for efficient storage of ternary data.

Ternary Data Encoding

Ternary values are encoded using 2 bits per trit in memory:

00= -1 (negative)01= 0 (zero)10= +1 (positive)11= reserved

This encoding enables 93.75% memory savings compared to 32-bit representation while maintaining fast access times.