Ternary RISC-V Core

Extending the lowRISC Ibex core with native ternary computing support and hardware-accelerated neural processing capabilities.

Project Overview

CI Status

Passing

Last run: 1/23/2026

Neural Speedup

3x

vs baseline implementation

Memory Reduction

93.75%

Ternary encoding efficiency

Efficiency Score

211.0

Overall performance index

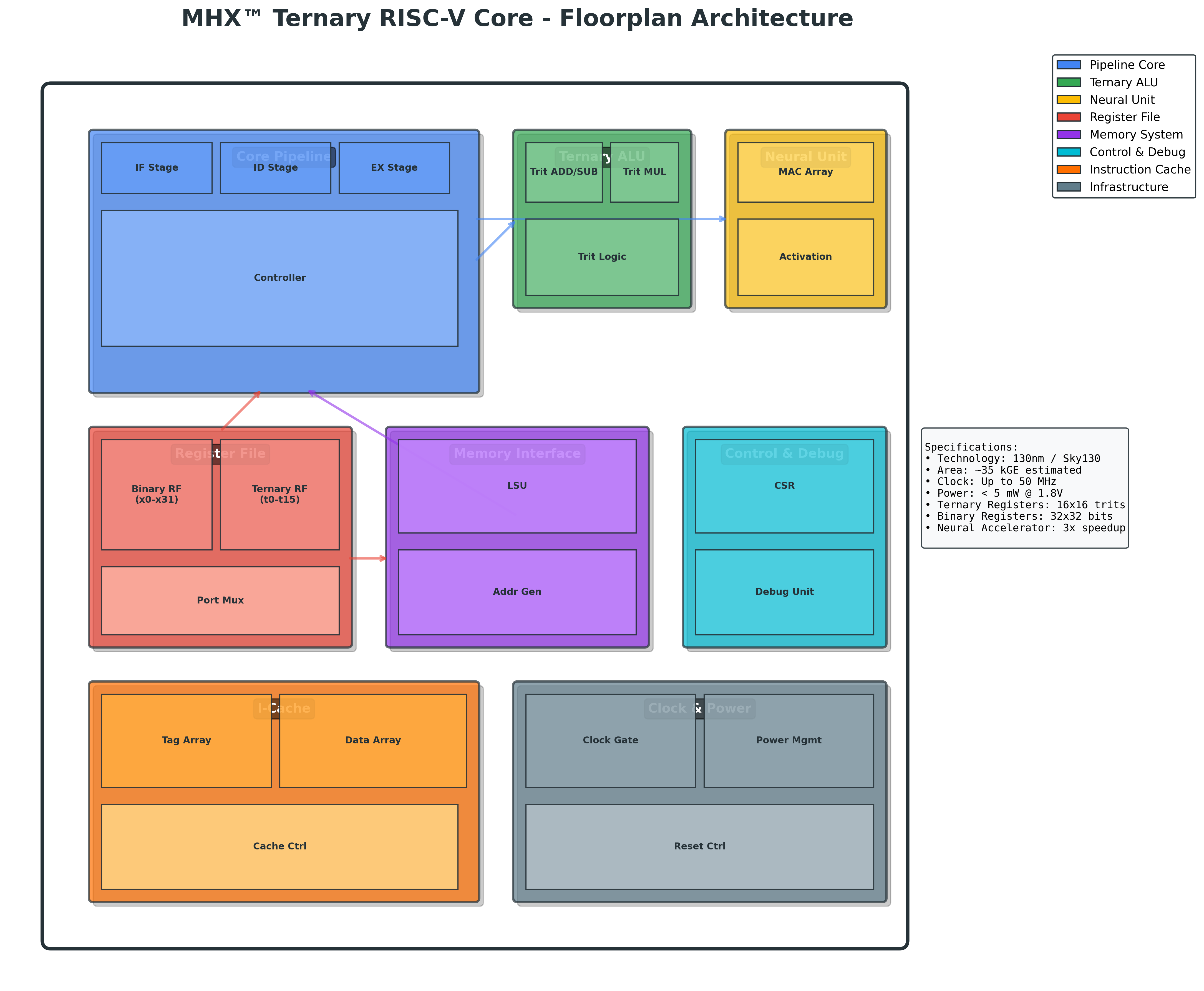

Floorplan Architecture

The MHX™ Core integrates seamlessly into the Ibex pipeline with dedicated ternary processing units, neural acceleration hardware, and a dual register file architecture.

Verification Status

Test Suites

RTL Linting (Verilator)

~2min

RTL Linting (Verible)

~1min

Ternary ALU Tests

All operations verified

Neural Unit Tests

MAC, activation functions

Register File Tests

Read/write integrity

Integration Tests

Full pipeline

Formal Verification

50+ assertions

Code Coverage

Coverage by Module

Performance Metrics

3x

Speedup vs software

2.13x

Speedup for matrix ops

70%

Estimated power savings